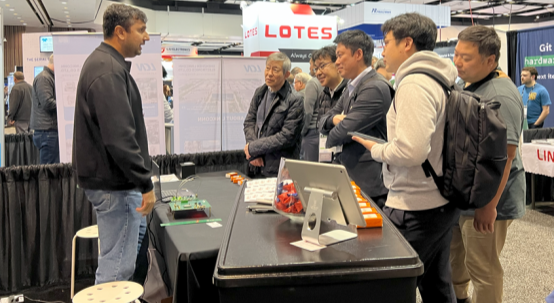

eTopus attended TSMC 2025 Symposium and showcased high-speed interface IP solutions

April 25, 2025

TSMC Symposium took place from April 23, 2025, at Santa Clara Convention Center, USA.

As a member of the TSMC IP Alliance, eTopus was invited to participate in this symposium at their partners pavilion and showed several innovative technologies, attracted attention from the industry.

▲TSMC IP Alliance

eTopus showcased a series of high-speed interface IP technologies, especially the high-speed SerDes and UCIe, which attracted industry experts, exhibitors, and spectators at theTSMC symposium.

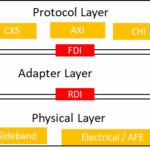

The UCIe IP solution is a multi-rate UCIe IP for low power and low latency Die-to-Die interconnection, which is designed for application scenarios such as HPC (High Performance Computing), data centers, CPUs, and accelerators.

The UCIe of eTopus strictly adheres to the UCIe 1.1/2.0 standard specifications and provides rich testing and monitoring functions, including Debug testing, CP/FT testing, error injection, real-time eye diagram scanning, and multiple Loopback modes. It uses control interface of APB/I2C/JTAG and can be configured as a single, Dual (x2) or Quad (x4) PHY module. In addition, it also supports x2 Stack to further enhance the edge bandwidth density.

eTopus 32G UCIe IP Highlights:

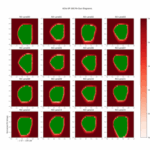

- Data Rate: 4, 8, 12, 16, 24, 32GT/s in SP mode

- single, Dual (x2) or Quad (x4) PHY module implementations with 16 lane configuration

- BER = 1E-15 @ 32GT/s without ECC

- Full UCIe SPEC compliance

- Very low latency

- High Energy Efficiency

- 3-dimensional de-skew units offer a full 2 UI of sweeping range to ease system integration

- IP orientation support: EW and NS

- Integrated test and debug features support wafer probe testing for identifying KGD

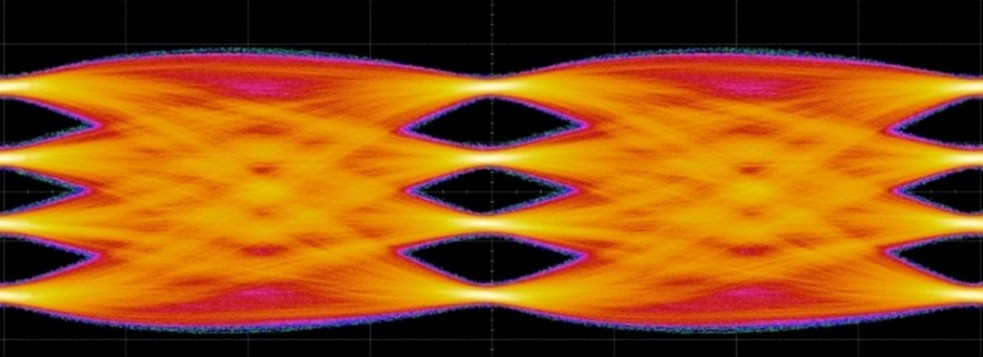

▲ RX 2D Eyes of all 16 lanes are widely open

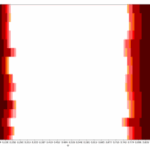

The eTopus 112G SerDes boasts powerful technical features. It has the capability of long reach transmission, which can meet the requirements of long reach signal transmission in scenarios such as Data centers, HPC, etc. It performs remarkably well in terms of power consumption, achieving low-power operation, which helps to reduce the overall energy consumption of the system. Meanwhile, it features low latency, effectively optimizing the signal transmission path and reducing signal distortion. By adopting an efficient clock synchronization mechanism, it provides a solid guarantee for latency-sensitive scenarios such as real-time data processing and large parameter model training.

eTopus 112G SerDes IP Highlights:

- Extra Long Reach (42dB) at 112G PAM4

- Low latency at different SerDes data rates from 1.25 to 112Gbps

- Low power: Channel-loss based Power scaling

- High reliability: ePRT™ equalizes any closed RX eyes, and achieves superior pre- and post-FEC Bit Error Rate, with minimal DFE error propagation

- Channel-loss based Power scaling

- Easy chip integration and bring-up: Proprietary performance tuning algorithm and extensive software API support

- RX Internal AC Coupling Capacitor

▲ 112G SerDes Eye diagram

eTopus continues to refine its products, expand its brand, and drive technological development to meet global industry demands. We aim to use high-speed interface ip technology to connect industries and support high data transmission to be more stable, more secure and more reliable.

About TSMC Symposium

The TSMC Symposium brings together leading enterprises and designers in the global semiconductor industry. It focuses on cutting-edge technologies such as advanced manufacturing processes, packaging, integrated circuits (ICs), and intellectual property (IPs). By strengthening the collaboration and linkage between the upstream and downstream of the industrial chain, it facilitates the transformation and application of technological innovation achievements, thereby driving the continuous development of the industry.